LA_M3P1

Laporan Akhir Modul 3 Percobaan 1

PERCOBAAN 1

1. Jurnal(DAFTAR ISI)

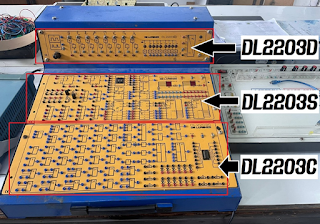

2. Hardware(DAFTAR ISI)

1. JK Flip-flop

2. Logic Probe

3. Clock

3. Video Praktikum(DAFTAR ISI)

4. Analisa(DAFTAR ISI)

Percobaan 1

1. Analisa sinyal output yang dikeluarkan masing-masing T-Flip flop? kenapa flip flop terakhir disebut MSB?

Ketika clock pertama menyala, hanay flip flop pertama yang akan toggle sehingga flip-flop pertama menghasilkan logika 1 dan flip-flop yang lain akan bernilai 0, sehingga outputnya 0 0 0 1 (1 dalam desimal). Ketika clock kedua menyala, T Flip-flop pertama akan toggle sehingga 1 akan menjadi 0 dan flip flop kedua akan toggle juga menjadi 0 ke 1, sehingga outputnya 0 0 1 0 (2 dalam desimal). Hal ini terus berlangsung sampai nilai-nilai bit menghitung ke atas sampai 15 dalam desimal. T flip-flop terakhir menghasilkan nilai paling besar, makannya T flip flop terakhir menjadi MSB.

2. Analisa falltime dan risetime pada clock terhadap output yang didapatkan?

Clock pada masing-masing T flip-flop yang kita gunakan active LOW, maka hanya fall time yang akan menggerakkan atau mengeksekusi data. Ketika sinyal Rise time masuk ke clock T flip-flop, maka data tetap tidak akan di eksekusi.

5. Link Download(DAFTAR ISI)

Download Datasheet JK Flip-flop

Komentar

Posting Komentar