LA M3 P2

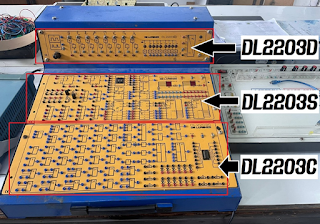

Laporan Akhir Modul 3 Percobaan 2 [KEMBALI KE MENU SEBELUMNYA] DAFTAR ISI Jurnal Hardware Video Rangkaian Analisa Link Download PERCOBAAN 2 1. Jurnal (DAFTAR ISI) 2. Hardware (DAFTAR ISI) 1. JK Flip-flop 2. Logic Probe 3. Clock 4. IC 74LS90 5. IC 7493 6. Ground 7. Power Supply 3. Video Praktikum (DAFTAR ISI) 4. Analisa (DAFTAR ISI) 1. Analisa dan jelaskan perbedaan pada percobaan 2a dengan pada percobaan 2b? Pada percobaan 2a clock A dan clock B menggunakan clock yang sama baik pada baik pada rangkaian 1 dan 2, dan menghasilkan angka 0 - 9 untuk rangkaian pertama dan 0 -15 pada rangkaian kedua secara tidak berurutan. Pada percobaan 2b clock B diinputkan dari Q0, sedangkan clock A saja yang diinputkan dari sumber clock. 2. Analisa dan jelaskan perbedaan input R9 dan R0? Input R0 Ketika kedua-duanya aktif maka akan menghasilkan nilai 0, sedangkan R9 jika kedua-keduanya aktif maka a...