LA_M4P2

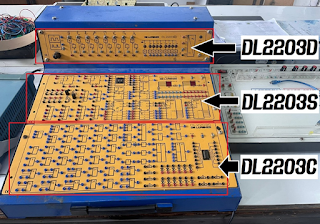

Laporan Akhir Modul 4 Percobaan 2 [KEMBALI KE MENU SEBELUMNYA] DAFTAR ISI Jurnal Hardware Video Rangkaian Analisa Link Download PERCOBAAN 2 1. Jurnal (DAFTAR ISI) 2. Hardware (DAFTAR ISI) 1. JK Flip-flop 2. Logic Probe 3. Clock 3. Video Praktikum (DAFTAR ISI) 4. Analisa (DAFTAR ISI) Percobaan 2 1. Analisa pengaruh LT, RBO, RBI, jika diaktifkan. Ketika LT aktif maka seluruh lampu akan aktif maka akan membentuk angka 8. RBO aktif akan membuat 7 segment mati karena RBO menahan data output ke 7 segment. RBI aktif akan menahan sinyal input sehingga jika ada perubahan bit penampil di 7 segment tidak berubah. 2. Analisa pengaruh BCD Decoder to sevent segment pada rangkaian! BCD to 7 segment mengubah nilai biner menjadi pin-pin 7 segment mana yang membentuk angka biner tersebut dalam decimal. Misalnya, ketika data 0001 (1 dalam decimal) masuk ke BCD to 7 segment akan menyalakan b ...